EE2L11 EPO-3: Design a Chip

Not running

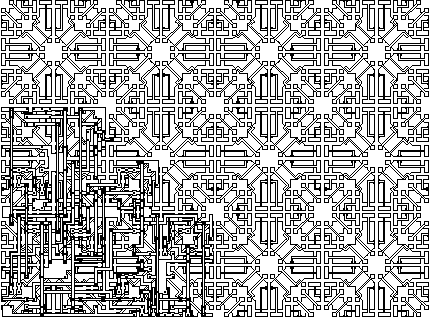

Topics: Structural hierarchical design of a VLSI chip, implemented using Sea-of-Gates

During this project, students make a VLSI design with a group. The project is a continuation of the projects during the first year of the bachelor program Electrical Engineering, but focusses more on structural hierarchical design and on working together within a group. The students are divided into groups of about 7-10 persons and each group together designs a chip.

After finishing this course, the student is able to

- make a design using global product specifications, including boundary conditions,

- design in a systematic hierarchical way,

- use analysis together with synthesis during the design process,

- analyse his design at different levels of abstraction,

- use different types of models during the design,

- take into account testability,

- perform the above design process within a group,

- make a design as a part of a group design,

- use modern computer tools during the design,

- make documentation about the design.

Teachers

Arjan van Genderen

dr. Massimo Mastrangeli (ECTM)

Organ-on-chip technology, micro/nanosystems assembly, capillary manipulation, solid-liquid interfaces

dr.ir. Sten Vollebregt (ECTM)

Graphene, carbon nanotubes, sensors, nanoparticles, wide bandgap semiconductors

Last modified: 2024-09-04

Details

| Credits: | 5 EC |

|---|---|

| Period: | 0/8/0/0 pr (not running) |

| Contact: | Massimo Mastrangeli |