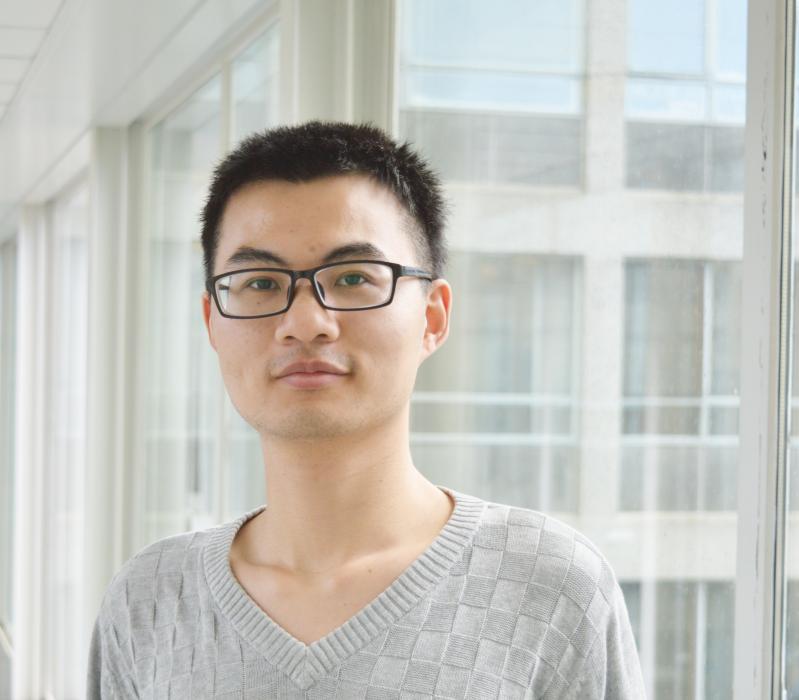

dr. Gong

Electronic Circuits and Architectures (ELCA), Department of Microelectronics

PhD thesis (Nov 2023): High-Performance Phase-Locked Loops for Quantum Computing Applications

Promotor: Masoud Babaie, Edoardo Charbon

Biography

Jiang Gong received the B.Sc. degree in Electrical Engineering from Jilin University, Changchun, China, in 2015, and the M.Sc. (cum laude) degree in Microelectronics from Delft University of Technology, Delft, the Netherlands, in 2017. He did his master thesis project at Holst Centre/imec, Eindhoven, the Netherlands, where he worked on low-power ring-oscillator-based fractional-N injection-locked digital PLL design for IoT applications. In 2017, he started the Ph.D. in cryogenic electronics for quantum applications at Delft University of Technology. His research interests include analog\mixed-signal IC design and cryogenic electronics for quantum computations.

Publications

- A Low-Spur Fractional-N PLL Based on a Time-Mode Arithmetic Unit

Gao, Zhong; He, Jingchu; Fritz, Martin; Gong, Jiang; Shen, Yiyu; Zong, Zhirui; Chen, Peng; Spalink, Gerd; Eitel, Ben; Alavi, Morteza S.; Staszewski, Robert Bogdan; Babaie, Masoud;

IEEE Journal of Solid-State Circuits,

pp. 1-20, 2022. DOI: 10.1109/JSSC.2022.3209338 - A 2.6-to-4.1GHz Fractional-N Digital PLL Based on a Time-Mode Arithmetic Unit Achieving -249.4dB FoM and -59dBc Fractional Spurs

Gao, Zhong; He, Jingchu; Fritz, Martin; Gong, Jiang; Shen, Yiyu; Zong, Zhirui; Chen, Peng; Spalink, Gerd; Eitel, Ben; Yamamoto, Ken; Staszewski, Robert Bogdan; Alavi, Morteza S.; Babaie, Masoud;

In 2022 IEEE International Solid- State Circuits Conference (ISSCC),

pp. 380-382, 2022. DOI: 10.1109/ISSCC42614.2022.9731561 - A Fractional-N Digitally Intensive PLL Achieving 428-fs Jitter and<-54-dBc Spurs Under 50-mV \$ \_ \pp\ \$ Supply Ripple

Chen, Yue; Gong, Jiang; Staszewski, Robert Bogdan; Babaie, Masoud;

IEEE Journal of Solid-State Circuits,

2021. - Equalization of OSDM over Time-Varying Channels Based on Diagonal-Block-Banded Matrix Enhancement

Jing Han; Yujie Wang; Zehui Gong; G. Leus;

Signal Processing,

Volume 168, pp. 107333, March 2020. - A 10-to-12 GHz 5 mW Charge-Sampling PLL Achieving 50 fsec RMS Jitter, -258.9 dB FOM and -65 dBc Reference Spur

Gong, Jiang; Sebastiano, Fabio; Charbon, Edoardo; Babaie, Masoud;

In 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC),

pp. 15-18, 2020. DOI: 10.1109/RFIC49505.2020.9218380 - 19.3 A 200dB FoM 4-to-5GHz Cryogenic Oscillator with an Automatic Common-Mode Resonance Calibration for Quantum Computing Applications

Gong, Jiang; Chen, Yue; Sebastiano, Fabio; Charbon, Edoardo; Babaie, Masoud;

In 2020 IEEE International Solid- State Circuits Conference - (ISSCC),

pp. 308-310, 2020. DOI: 10.1109/ISSCC19947.2020.9062913 - Benefits and challenges of designing cryogenic CMOS RF circuits for quantum computers

Mehrpoo, M; Patra, B; Gong, J; van Dijk, JPG; Homulle, H; Kiene, G; Vladimirescu, A; Sebastiano, F; Charbon, E; Babaie, M; others;

In 2019 IEEE International Symposium on Circuits and Systems (ISCAS),

IEEE, pp. 1--5, 2019. - A 1.33 mW, 1.6 ps rms-Integrated-Jitter, 1.8-2.7 GHz Ring-Oscillator-Based Fractional-N Injection-Locked DPLL for Internet-of-Things Applications

Gong, Jiang; He, Yuming; Ba, Ao; Liu, Yao-Hong; Dijkhuis, Johan; Traferro, Stefano; Bachmann, Christian; Philips, Kathleen; Babaie, Masoud;

In 2018 IEEE Radio Frequency Integrated Circuits Symposium (RFIC),

IEEE, pp. 44--47, 2018. - Time estimation with multichannel digital silicon photomultipliers

E. Venialgo; S. Mandai; T. Gong; D.R. Schaart; E. Charbon;

Physics in Medicine and Biology,

Volume 60, Issue 6, pp. 2435-2452, Mar. 2015. DOI: 10.1088/0031-9155/60/6/2435

document - A 67,392 SPAD PVTB-Compensated Multi-Channel Digital SiPM with 432 Column-Parallel 48ps 17-bit TDCs for Endoscopic Time-of-flight PET

A.J. Carimatto; S. Mandai; E. Venialgo; T. Gong; G. Borghi; D. Schaart; E. Charbon;

In IEEE International Solid-State Circuits Conference,

Feb. 2015.

document - Practical Time Mark Estimators for Multichannel Digital Silicon Photomultipliers

E. Venialgo; S. Mandai; T. Gong; D. Schaart; E. Charbon;

In IEEE Nuclear Science Symposium,

Nov. 2015.

document - FPGA Based Fast Gamma-Ray Time Mark Estimator for Ultra-Miniature Endoscopic PET Applications

T. Gong; S. Mandai; E. Venialgo; A.J. Carimatto; E. Charbon;

In IEEE Nuclear Science Symposium,

Nov. 2014.

BibTeX support

Last updated: 26 Apr 2024

Jiang Gong

Alumnus- Left in 2021

- Now: Senior analog/mixed signal IC designer at SiTime