MSc thesis project proposal

Fully Integrated Piezoelectric Energy Harvesting for Self-Sustained IoT Sensors

Due to the large number of ubiquitously distributed IoT sensors, chemical batteries become very unpractical when replacing/recharging them. In order to make sensors self-sustained, harvesting ambient energy provides a promising solution to power the sensors continuously.

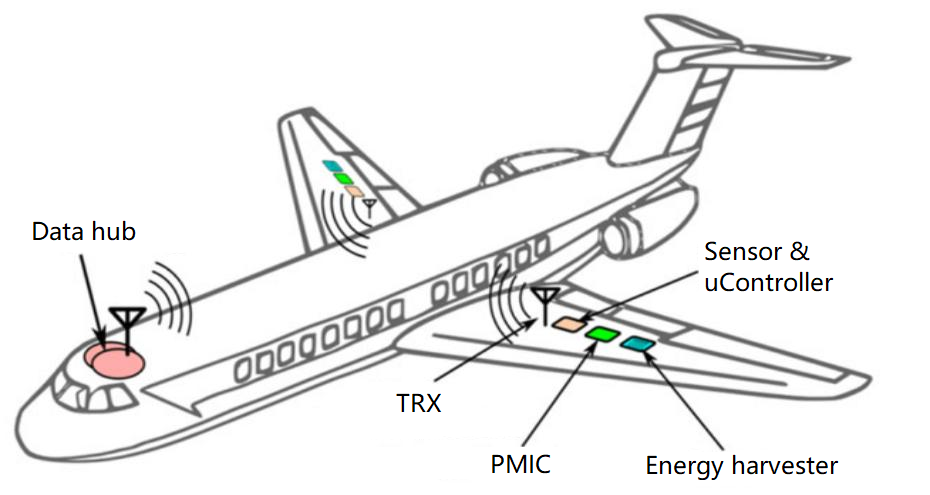

Amongst different energy harvesting topologies, piezoelectric energy harvesting provides a stable power source where there are mechanical vibrations. Compared to other topologies, the vibration energy harvesters can be implemented in places where there is no sunlight or wind. These harvesters are particularly useful when implemented in aircrafts, cars, bikes, bridges, tunnels, buildings, human bodies, etc.

Several piezoelectric energy harvesting techniques have been proposed to increase the energy efficiency and deal with irregular vibrations. However, most of these techniques usually require one or more large off-chip inductors or off-chip capacitors to achieve high energy efficiency, which is counter to miniaturization [1]. A technique that does not require any off-chip component is the key to achieve a fully integrated energy harvesting design, to minimize the form factor for the self-sustained sensors to be implemented in space-limited places [2].

[1] Y. K. Ramadass and A. P. Chandrakasan, "An Efficient Piezoelectric Energy Harvesting Interface Circuit Using a Bias-Flip Rectifier and Shared Inductor," IEEE JSSC, vol. 45, no. 1, pp. 189-204, 2010.

[2] S. Du and A. A. Seshia, "An Inductorless Bias-Flip Rectifier for Piezoelectric Energy Harvesting," IEEE JSSC, vol. 52, no. 10, pp. 2746-2757, 2017.

Assignment

The idea is to design a fully integrated piezoelectric energy harvesting interface circuit, which provides high energy efficiency, cold startup ability, maximum power point tracking (MPPT) and self-sustainability on a single chip. The design will be implemented in CMOS technology and verified with post-layout simulations. Tape-out is possible depending on the design and available time.Requirements

Student should be familiar with analog IC design and Cadence environment.Contact

dr. Sijun Du

Electronic Instrumentation Group

Department of Microelectronics

Last modified: 2021-11-11