MSc thesis project proposal

Low Power Bluetooth Transceiver with a RISC-V Core for Autonomous Sensors

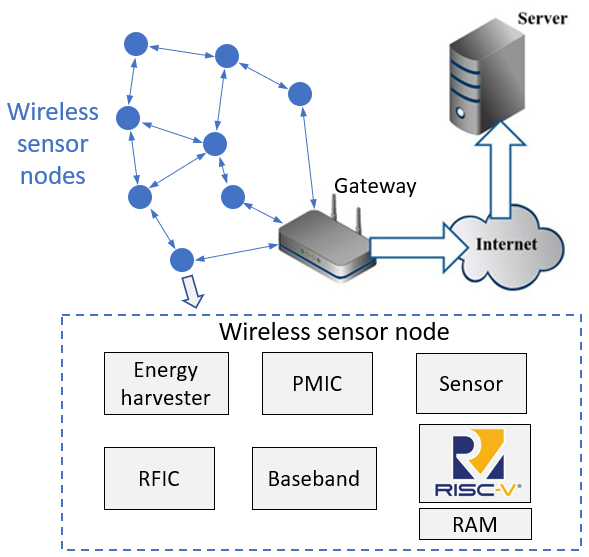

Digital circuits and microprocessors play important roles in all electronic devices. While some applications require digital systems to achieve high computation capability with low latency, many other applications require well-balanced digital systems consuming ultra-low power when they are employed in Internet-of-Things (IoT) sensors, biomedical implants, wearable devices, etc.

While most of current digital circuits are designed in Verilog or VHDL, all digital designs in this project will be written in Chisel [1]. Instead of building the digital hardware directly, we will use Chisel to build a highly parameterized digital hardware generator. Chisel is a hardware construction language, which is very easy to learn with graduate-level digital IC design background (Verilog or VHDL). For a new Chisel learner, it only takes 1-2 weeks to start designing the first Chisel circuit, and 1-2 months to start building large complex DSP and RISC-V systems. Chisel allows designers to build a hardware in much less time and the Chisel generator can generate different flavors of hardware according to applications. Designers can use Chisel to implement highly customized RISC-V cores easily and the entire Chisel ecosystem is open-source. Chisel and the Chisel-based digital design methodology are drawing more and more industrial interests and have been employed for designing digital systems in several world-leading companies, e.g., Tensor Processing Unit (TPU) by Google.

In this project, we are going to use Chisel to design an 802.15.4 compatible Bluetooth Low Energy (BLE) baseband integrated with a RISC-V core for autonomous wireless sensor applications. Users can run-time configure the DSP and RISC-V core, and upgrade firmware via Bluetooth.

[1] Chisel: Constructing Hardware in a Scala Embedded Language. URL: http://chisel.eecs.berkeley.edu/

Assignment

1. Get familiar with Chisel hardware construction language and literature review of BLE baseband and RISC-V microprocessor. Student will be introduced to build connections with labs at UC Berkeley for Chisel-related problem-shooting. 2. Design the BLE baseband and RISC-V system with Chisel. 3. Integrate the system to meet performance and power requirements. The system should enable run-time configurability via Bluetooth.Requirements

Student should be familiar with digital IC design. Prior experience on Chisel is not required.Contact

dr. Sijun Du

Electronic Instrumentation Group

Department of Microelectronics

Last modified: 2021-11-11